A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

### A Novel Method of Cascaded H-Bridge Multi Level Inverter for Industrial Applications

#### **U CHAITANYA**

Assistant Professor

Department of Electrical & Electronics Engineering,

G. Pullaiah College of Engineering and Technology,

Pasupula Village, Nandikotkur Rd, near Venkayapalle,

Kurnool, Andhra Pradesh 518002.

### M.Bhagya Lakshmi

**Assistant Professor**

Department of Electrical & Electronics Engineering, G. Pullaiah College of Engineering and Technology, Pasupula Village, Nandikotkur Rd, near Venkayapalle, Kurnool, Andhra Pradesh 518002.

Abstract-A new topology of cascaded multilevel converter is proposed. The proposed topology is based on a cascaded connection of single-phase sub multilevel converter units and full-bridge converters. Compared to the conventional multilevel converter, the number of dc voltage sources, switches, installation area, and converter cost is significantly reduced as the number of voltage steps increases. In order to calculate the magnitudes of the required dc voltage sources, three methods are proposed. Then, the structure of the proposed topology is optimized in order to utilize a minimum number of switches and dc voltage sources, and produce a high number of output voltage steps. The prior H-bridge based multilevel inverter can increase the number of output voltage levels by adding switch components and DC input voltage sources. If it employs seven switches and three DC sources, the number of output voltage levels becomes seven. Although its THD characteristics are improved. To mitigate this problem, we propose an efficient PWM switching method for the prior H-bridge based multilevel inverter. The operation and performance of the proposed a single-phase 31-level converter with multilevel converter is verified by MATLAB/ SIMULINK.

#### I. INTRODUCTION

Over many years, Induction motor drives have been popularly used for variable speed control applications in industries. This is because the induction motor is simple in construction and requires less maintenance. In recent times, multilevel inverters (MLI) are gaining popularity and widely used for induction motor drive applications [1-3]. It is especially used for medium to high voltage and high current drive applications. There are many advantages of multilevel inverters as compared to conventional inverters. Main advantages are low total harmonics distortion (THD), low switching losses, good power quality and reduced electromagnetic interference (EMI). Main feature of multilevel inverter is that it reduces voltage stress on each component [4-8]. The topologies of multilevel inverters are classified into three types. They are flying capacitor, diode clamped and Hbridge cascaded multilevel inverters.

Cascaded H-bridge (CHB) multilevel inverter is one of the most popular inverter topology used in high-power medium voltage (MV) drives. It is composed of a multiple units of single-phase H-bridge power cells. In practice, the number of power cells in a CHB inverter is mainly determined by its operating voltage and manufacturing cost. Cascaded H-bridge multilevel inverter requires the least number of components for the same voltage level as compared to all three types of inverter [9-11]. The growth of multilevel inverter caused development of various modulation schemes. The most common initial

application of multilevel converters has been in traction, both in locomotives and track-side static converters. More recent applications have been for power system converters for VAR compensation and stability enhancement, active filtering, high-voltage motor drive, high-voltage dc transmission and most recently for medium voltage induction motor variable speed drives. Many multilevel converter applications focus on industrial medium-voltage motor drives, utility interface for renewable energy systems, Flexible AC Transmission System (FACTS) and traction drive systems.

In recent years, multilevel inverters have received more attention in industrial applications, such as motor drives, static VAR compensators and renewable energy systems. Compared to the traditional two-level voltage source inverters, the stepwise output voltage is the major advantage of multilevel inverters.

### II. PROPOSED TOPOLOGY

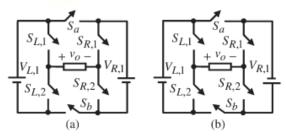

In Fig.1, two new topologies are proposed for a seven-level inverter. As shown in. 1, the proposed topologies are obtained by adding two unidirectional power switches and one dc voltage source to the H-bridge inverter structure. In other words, the proposed inverters are comprised of six untidier tonal power switches (Sa, Sb, SL,1, SL,2, SR,1, and SR,2) an two dc voltage sources (VL,1 andVR,1). In this paper, these topologies are called developed H-bridge. As shown in Fig.1, the simultaneous turn-on of SL,1 and SL,2(orSR,1and SR,2)

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

Fig.1.Proposed seven-level inverters. (a) First proposed topology. (b) Second Proposed topology.

### TABLE I OUTPUT VOLTAGES OF THE PROPOSED SEVEN-LEVEL INVERTERS

| No. | $S_{L,1}$ | $S_{L,2}$ | $S_{R,1}$ | $S_{R,2}$ | $S_a$ | $S_b$ | ν <sub>0</sub> (Fig. 1(a)) | ν <sub>o</sub> (Fig. 1(b)) |

|-----|-----------|-----------|-----------|-----------|-------|-------|----------------------------|----------------------------|

| 1   | 1         | 0         | 0         | 1         | 0     | 1     | $V_{L,1}$                  | $V_{L,1}$                  |

| 2   | 1         | 0         | 0         | 1         | 1     | 0     | $V_{R,1}$                  | $-V_{R,1}$                 |

| 3   | 1         | 0         | 1         | 0         | 0     | 1     | $V_{L,1} - V_{R,1}$        | $V_{L,1} + V_{R,1}$        |

| 4   | 1         | 0         | 1         | 0         | 1     | 0     | 0                          | 0                          |

|     | 0         | 1         | 0         | 1         | 0     | 1     |                            |                            |

| 5   | 0         | 1         | 1         | 0         | 1     | 0     | $-V_{L,1}$                 | $-V_{L,1}$                 |

| 6   | 0         | 1         | 1         | 0         | 0     | 1     | $-V_{R,1}$                 | $V_{R,1}$                  |

| 7   | 0         | 1         | 0         | 1         | 1     | 0     | $-(V_{L,1} - V_{R,1})$     | $-(V_{L,1}+V_{R,1})$       |

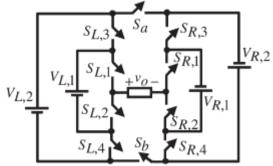

Causes the voltage sources to short-circuit. Therefore, the simultaneous turn-on of the mentioned switches must be avoided. In addition, Sa and Sb should not turn on, simultaneously. The difference in the topologies illustrated in Fig.1 is in the connection of the dc voltage sources polarity. Table I shows the output voltages of the proposed inverters for different states of the switches. In this table, 1 and 0 indicate the ON- and OFF-states of the switches, respectively. As it is obvious from Table I, if the values of the dc voltage sources are equal, the number of voltage levels decreases to three. Therefore, the values of dc voltage sources should be different to generate more voltage levels without increasing the number of switches and dc voltage sources. Considering Table I, to generate all voltage levels (odd and even) in the proposed topology shown in Fig.1(a), the magnitudes of  $V_{L,1}$  and  $V_{R,1}$  should be considered 3puand 1pu, respectively. Similarly, for the topology shown in Fig.1 (a), the magnitudes of  $V_L$ , 1andV<sub>R</sub>, 1 should be considered 2pu and 1pu, respectively. Considering the aforementioned explanations, the total cost of the proposed topology in Fig.1(b) is low because dc voltage sources with low magnitudes are needed. By developing the seven-level inverter shown in Fig.1 (b), the 31-level inverter shown in Fig.2 can be proposed. This topology consists of ten unidirectional power switches and four dc voltage sources. According to Fig. 2, if the power switches of  $(S_{L,1},S_{L,2})$ ,  $(S_{L,3},S_{L,4})$ ,  $(S_{R,1},S_{R,2})$ , and  $(S_{R,3},S_{R,4})$ turn on simultaneously, the dc voltage sources of  $V_{L,1}$ ,  $V_{L,2}$ ,  $V_{R,1}$ , and  $V_{R,2}$  will be short-circuited, respectively. Therefore, the simultaneous turn-on of these switches should be avoided. In addition, Sa and Sb should not turn on simultaneously. It is important to note that the 31-level topology can be provided through the structure presented in Fig.1(a), where the only difference will be in the polarity of the applied dc voltage sources. By developing the proposed 31-level inverter. This topology

Fig.2. Proposed 31-level inverter.

$$N_{\text{step}} = 2^{2n+1} - 1$$

(1)

$$N_{\text{switch}} = 4n + 2$$

(2)

$$N_{\text{source}} = 2n$$

(3)

$$V_{o,\max} = V_{L,n} + V_{R,n}. \tag{4}$$

The other important parameters of the total cost of a multilevel inverter for evaluation are the variety of the values of dc voltage sources and the value of the blocking voltage of the switches. As the variety of dc voltage sources and the value of the blocking voltage of the switches are low, the inverter's total cost decreases [20]. The number of variety of the values of dc voltage sources (Variety) is given by

$$N_{\text{variety}} = 2n.$$

(5)

The following pattern is utilized to calculate the maximum magnitude of the blocking voltage of the power switches. As shown in Fig.1 (b), the blocking voltage of SR, 1 and SR, 2 are calculated as follows:

$$V_{SR,1} = V_{SR,2} = V_{R,1}$$

(6)

Where VSR,1 and VSR,2 indicate the maximum blocking voltages of SR,1 and SR,2, respectively. The blocking voltage of SL, 1 and SL, 2 are as follows

$$V_{\rm SL,1} = V_{\rm SL,2} = V_{L,1}$$

(7)

A peer reviewed international journal ISSN: 2457-0362

www.ijarst.in

IJARST

Where VSL, 1 and VSL, 2 indicate the maximum blocking voltages of SL, 1andSL,2, respectively. Therefore, the maximum blocking voltage of all switches in the proposed seven-level inverter (Vblock,1)is calculated as follows

$$\begin{split} V_{\text{block},1} &= V_{\text{SR},1} + V_{\text{SR},2} + V_{\text{SL},1} + V_{\text{SL},2} + V_{\text{Sa}} + V_{\text{Sa}} \\ &= 4(V_{R,1} + V_{L,1}). \end{split} \tag{8}$$

Considering Fig.2, the maximum blocking voltage of the switches is as follows

$$V_{SR,1} = V_{SR,2} = V_{R,1}$$

(9)

$$V_{SR,3} = V_{SR,4} = V_{R,2} - V_{R,1}$$

(10)

$$V_{SL,1} = V_{SL,2} = V_{L,1}$$

(11)

$$V_{\text{SL},3} = V_{\text{SL},4} = V_{L,2} - V_{L,1}$$

(12)

$$V_{\text{Sa}} = V_{\text{Sb}} = V_{R,2} + V_{L,2}.$$

(13)

Therefore, the maximum blocking voltage of all switches of the proposed 31-level inverter (Vblock, 2) is as follows

$$V_{\text{block},2} = V_{\text{SR},1} + V_{\text{SR},2} + V_{\text{SR},3} + V_{\text{SR},4} + V_{\text{SL},1} + V_{\text{SL},2}$$

$$+ V_{\text{SL},3} + V_{\text{SL},4} + V_{\text{Sa}} + V_{\text{Sb}}$$

$$= 4(V_{R,2} + V_{L,2}).$$

(14)

Similarly, the maximum blocking voltage of all switches of the 127-level inverter is calculated as follow

$$V_{\text{block},3} = 4(V_{R,3} + V_{L,3}).$$

(15)

Finally, the maximum blocking voltage of all the switches of the general topology (Vblock, n) is calculated as follows:

$$V_{\text{block},n} = 4(V_{R,n} + V_{L,n}).$$

(16)

### III. PERFORMANCE OF THE INDUCTION **MOTOR**

The sinusoidally-distributed flux density wave produced by the stator magnetizing currents sweeps past the rotor conductors, it generates a voltage in them. The result is a sinusoidally-distributed set of currents in the short-circuited rotor bars. Because of the low resistance of these shorted bars, only a small relative angular velocity, r, between the angular velocity, s, of the flux wave and the mechanical angular velocity of the two-pole rotor is required to produce

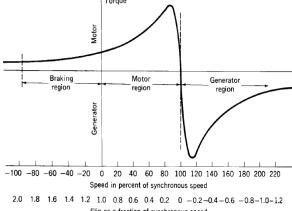

the necessary rotor current. The relative angular velocity, r, is called the slip velocity. The interaction of the sinusoidally-distributed air gap flux density and induced rotor currents produces a torque on the rotor. The typical induction motor speed-torque characteristic is shown in Figure.

Slip as a fraction of synchronous speed

Fig.3, speed-torque characteristics of induction motor. An induction motor (IM) is a type of asynchronous AC motor where power is supplied to the rotating device by means of electromagnetic induction. An electric motor convert's electrical power to mechanical power in its rotor. There are several ways to supply power to the rotor. In a DC motor this power is supplied to the armature directly from a DC source, while in an induction motor this power is induced in the rotating device. An induction motor is sometimes called a rotating transformer because the stator (stationary part) is essentially the primary side of the transformer and the rotor (rotating part) is the secondary side. Induction motors are widely used, especially poly phase induction motors, which are frequently used in industrial drives. When induction motors are given supply, they draw the current as

$$I_a = \frac{Ea - Eb}{Ra}$$

As initially  $E_b = 0$

Motor draws a very high current initially; due to which voltage dip will forms, which show the effect on the power system network. In order to avoid such problems a effective controlled APF is placed without effecting the power quality or the motor performance characteristics.

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

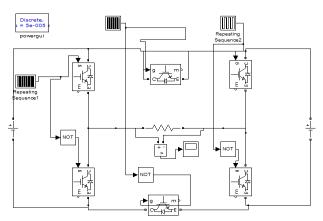

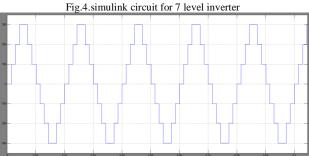

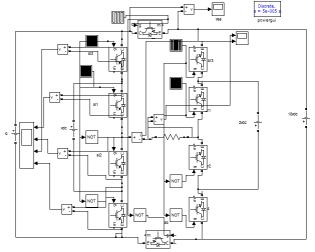

### IV.MATLAB/SIMULINK RESULTS

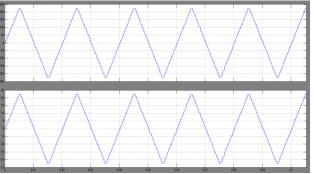

Fig.5.Simulation results for 7 level inverter

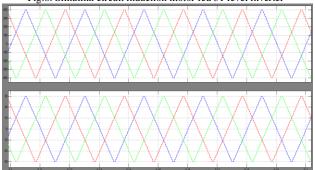

Fig.6.Simulation results for 31 level inverter

Fig.7.Simulation results voltage and current for 31 level inverter

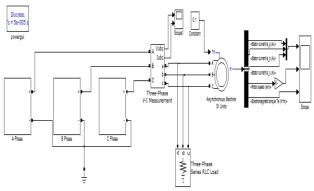

Fig.8. Simulink circuit induction motor fed 31 level inverter

Fig.9.Simulation results for three phase voltage and current

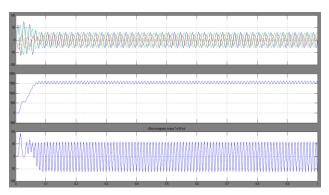

Fig.10. Simulation results for motor characteristics

A peer reviewed international journal

www.ijarst.in

ISSN: 2457-0362

#### IV.CONCLUSION

In this paper, two basic topologies have been proposed for multilevel inverters to generate seven voltage levels at the output. The basic topologies can be developed to any number of levels at the output where the 31-level and general topologies are consequently presented. In addition, a new algorithm to determine the magnitude of the dc voltage sources has-been proposed. The proposed general topology was compared with the different kinds of presented topologies in literature from different points of view. According to the comparison re salts, the proposed topology requires a lesser number of IGBTs, power diodes, driver circuits, and dc voltage sources. Moreover, the magnitude of the blocking voltage of the switches is lower than that of conventional topologies. However, the proposed topology has a higher number of varieties of dc voltage sources in comparison with the others. The proposed topology was verified through the matlab/Simulink platform for 31-level inverter with induction motor drive.

### **REFERENCES**

- [1] E. Babaei and S. H. Hussein, "Charge balance control methods for say metrical cascade multilevel converters," in Proc. ICEMS, Seoul, Korea, 2007, pp. 74–79.

- [2] K. Wang, Y. Li, Z. Zheng, and L. Xu, "Voltage balancing and fluctuation suppression methods of floating capacitors in a new modular multilevel converter," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1943–1954, May 2013.

- [3] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new topology of cascaded multilevel converters with reduced number of components for high-voltage applications," IEEE Trans. Power Electron., vol. 26, no. 11, pp. 3109–3118, Nov. 2011.

#### **AUTHOR'S PROFILE**

G.ARUN KUMAR YADAV received B.Tech degree in Electrical and Electronics from Jayamukhi Institute of Technology & Sciences, JNTUH University, Warangal in 2010. he is currently pursuing M.Tech degree in Power Electronics from Malla reddy Institute of Engineering & Technology ,JNTUH.

N.V.KOTESWARA RAO received his B.Tech, and M.Tech degrees from the Chirala Engineering College and Malla reddy Engineering College JNTUH University, Chirala and Hyderabad in 2009 and 2012 respectively. Currently he is working as Professor in the Department of Electrical and Electronics Engineering at Malla reddy Institute of Engineering & Technology, Hyderabad.

- [4] M. Manjrekar and T. A. Lipo, "A hybrid multilevel inverter topology for drive application," in Proc. APEC, 1998, pp. 523–529.

- [5] M. Narimani and G. Moschopoulos, "A novel single-stage multilevel type full-bridge converter," IEEE Trans. Ind. Electron., vol. 60, no. 1, pp. 31–42, Jan. 2013.

- [6] N. Abd Rahim, M. F. Mohamad Elias, and W. P. Hew, "Transistor-clamped H-bridge based cascaded multilevel inverter with new method of capacitor voltage balancing," IEEE Trans. Ind. Electron., vol. 60, no. 8, pp. 2943–2956, Aug. 2013.

- [7] M. Farhadi Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of submultilevel inverters," IEEE Trans.Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

- [8] S. R. Pulikanti, G. Konstantin, and V. G. Agelidis, "Hybrid seven-level cascaded active neutral-point-clamped-based multilevel converter under SHE-PWM,"IEEE Trans. Ind. Electron., vol. 60, no. 11, pp. 4794–4804, Nov. 2013.

- [9] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel dc voltage sources," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

- [10] G. Waltrich and I. Barbi, "Three-phase cascaded multilevel inverter using power cells with two inverter legs in series," IEEE Trans. Ind. Appl., vol. 57, no. 8, pp. 2605–2612, Aug. 2010.

- [11] W. K. Choi and F. S. Kang, "H-bridge based multilevel inverter using PWM switching functions," inProc. INTELEC, 2009, pp. 1–5.

[12] E. Babaei, M. Farhadi Kangarlu, and F. Najaty Mazgar,

- [12] E. Babaei, M. Farhadi Kangarlu, and F. Najaty Mazgar, "Symmetricand asymmetric multilevel inverter topologies with reduced switching devices," Elect. Power Syst. Res., vol. 86, pp. 122–130, May 2012.

- [13] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel con verter topology with reduced number of power electronic components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 655–667, Feb. 2012.

- [14] E. Babaei, S. H. Hussein, G. B. Gharehpetian, M. Tarafdar Hague, and M. Sabah, "Reduction of DC voltage sources and switches in asymmetry cal multilevel converters using a novel topology, "Elect. Power Syst. Res., vol. 77, no. 8, pp. 1073–1085, Jun. 2007.

- [15] E. Babaei and S. H. Hussein, "New cascaded multilevel inverter topology with minimum number of switches, "Energy Convers. Manage. vol. 50, no. 11, pp. 2761–2767, Nov. 2009.